I speak Spanish to God, Italian to women, French to men, and German to my horse.

Charles V, King of France 1337-1380

# Instructions: Language of the Computer

| <b>4.1</b> | introduction 70                      |   |

|------------|--------------------------------------|---|

| 2.2        | Operations of the Computer Hardware  | 7 |

| 2.3        | Operands of the Computer Hardware 80 | ) |

| 2.4        | Signed and Unsigned Numbers 87       |   |

| 2.5        | Representing Instructions in the     |   |

|            | Computer 94                          |   |

**2.6 Logical Operations** 102

**2.7** Instructions for Making Decisions 105

Ψ

| 2.8           | Supporting Procedures in Computer Hardware 112               |

|---------------|--------------------------------------------------------------|

| 2.9           | Communicating with People 122                                |

| 2.10          | MIPS Addressing for 32-Bit Immediates and Addresses 128      |

| 2.11          | <b>Parallelism and Instructions: Synchronization</b> 137     |

| 2.12          | Translating and Starting a Program 139                       |

| 2.13          | A C Sort Example to Put It All Together 149                  |

| 2.14          | Arrays versus Pointers 157                                   |

| <b>2.15</b>   | Advanced Material: Compiling C and Interpreting Java $\ 161$ |

| 2.16          | Real Stuff: ARM Instructions 161                             |

| 2.17          | Real Stuff: x86 Instructions 165                             |

| 2.18          | Fallacies and Pitfalls 174                                   |

| 2.19          | Concluding Remarks 176                                       |

| <b>0</b> 2.20 | Historical Perspective and Further Reading 179               |

| 2.21          | Exercises 179                                                |

## The Five Classic Components of a Computer

# 2.1

#### Introduction

instruction set The vocabulary of commands understood by a given architecture.

To command a computer's hardware, you must speak its language. The words of a computer's language are called *instructions*, and its vocabulary is called an **instruction set**. In this chapter, you will see the instruction set of a real computer, both in the form written by people and in the form read by the computer. We introduce instructions in a top-down fashion. Starting from a notation that looks like a restricted programming language, we refine it step-by-step until you see the real language of a real computer. Chapter 3 continues our downward descent, unveiling the hardware for arithmetic and the representation of floating-point numbers.

You might think that the languages of computers would be as diverse as those of people, but in reality computer languages are quite similar, more like regional dialects than like independent languages. Hence, once you learn one, it is easy to pick up others. This similarity occurs because all computers are constructed from hardware technologies based on similar underlying principles and because there are a few basic operations that all computers must provide. Moreover, computer designers have a common goal: to find a language that makes it easy to build the hardware and the compiler while maximizing performance and minimizing cost and power. This goal is time honored; the following quote was written before you could buy a computer, and it is as true today as it was in 1947:

It is easy to see by formal-logical methods that there exist certain [instruction sets] that are in abstract adequate to control and cause the execution of any sequence of operations.... The really decisive considerations from the present point of view, in selecting an [instruction set], are more of a practical nature: simplicity of the equipment demanded by the [instruction set], and the clarity of its application to the actually important problems together with the speed of its handling of those problems.

Burks, Goldstine, and von Neumann, 1947

The "simplicity of the equipment" is as valuable a consideration for today's computers as it was for those of the 1950s. The goal of this chapter is to teach an instruction set that follows this advice, showing both how it is represented in hardware and the relationship between high-level programming languages and this more primitive one. Our examples are in the C programming language; Section 2.15 on the CD shows how these would change for an object-oriented language like Java.

By learning how to represent instructions, you will also discover the secret of computing: the **stored-program concept**. Moreover, you will exercise your "foreign language" skills by writing programs in the language of the computer and running them on the simulator that comes with this book. You will also see the impact of programming languages and compiler optimization on performance. We conclude with a look at the historical evolution of instruction sets and an overview of other computer dialects.

The chosen instruction set comes from MIPS Technologies, which is an elegant example of the instruction sets designed since the 1980s. Later, we will take a quick look at two other popular instruction sets. ARM is quite similar to MIPS, and more than three billion ARM processors were shipped in embedded devices in 2008. The other example, the Intel x86, is inside almost all of the 330 million PCs made in 2008.

We reveal the MIPS instruction set a piece at a time, giving the rationale along with the computer structures. This top-down, step-by-step tutorial weaves the components with their explanations, making the computer's language more palatable. Figure 2.1 gives a sneak preview of the instruction set covered in this chapter.

stored-program

concept The idea that

instructions and data of

many types can be stored

in memory as numbers,

leading to the storedprogram computer.

## 2.2

## **Operations of the Computer Hardware**

Every computer must be able to perform arithmetic. The MIPS assembly language notation

```

add a, b, c

```

instructs a computer to add the two variables b and c and to put their sum in a.

This notation is rigid in that each MIPS arithmetic instruction performs only one operation and must always have exactly three variables. For example, suppose we want to place the sum of four variables b, c, d, and e into variable a. (In this section we are being deliberately vague about what a "variable" is; in the next section we'll explain in detail.)

The following sequence of instructions adds the four variables:

```

add a, b, c # The sum of b and c is placed in a. add a, a, d # The sum of b, c, and d is now in a. add a, a, e # The sum of b, c, d, and e is now in a.

```

Thus, it takes three instructions to sum the four variables.

The words to the right of the sharp symbol (#) on each line above are *comments* for the human reader, and the computer ignores them. Note that unlike other programming languages, each line of this language can contain at most one instruction. Another difference from C is that comments always terminate at the end of a line.

There must certainly be instructions for performing the fundamental arithmetic operations.

Burks, Goldstine, and von Neumann, 1947

#### **MIPS operands**

| Name                            | Example                                                                                | Comments                                                                                                                                                                                      |

|---------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32 registers                    | \$s0-\$s7, \$t0-\$t9, \$zero,<br>\$a0-\$a3, \$v0-\$v1, \$gp, \$fp,<br>\$sp, \$ra, \$at | Fast locations for data. In MIPS, data must be in registers to perform arithmetic, register \$zero always equals 0, and register \$at is reserved by the assembler to handle large constants. |

| 2 <sup>30</sup> memory<br>words | Memory[0], Memory[4], ,<br>Memory[4294967292]                                          | Accessed only by data transfer instructions. MIPS uses byte addresses, so sequential word addresses differ by 4. Memory holds data structures, arrays, and spilled registers.                 |

#### **MIPS** assembly language

| Category         | Instruction                      | Example             | Meaning                                     | Comments                              |

|------------------|----------------------------------|---------------------|---------------------------------------------|---------------------------------------|

|                  | add                              | add \$s1,\$s2,\$s3  | \$s1 = \$s2 + \$s3                          | Three register operands               |

| Arithmetic       | subtract                         | sub \$s1,\$s2,\$s3  | \$s1 = \$s2 - \$s3                          | Three register operands               |

|                  | add immediate                    | addi \$s1,\$s2,20   | \$s1 = \$s2 + <b>20</b>                     | Used to add constants                 |

|                  | load word                        | lw \$s1,20(\$s2)    | \$s1 = Memory[\$s2 + 20]                    | Word from memory to register          |

|                  | store word                       | sw \$s1,20(\$s2)    | Memory[\$s2 + 20] = \$s1                    | Word from register to memory          |

|                  | load half                        | lh \$s1,20(\$s2)    | \$s1 = Memory[\$s2 + 20]                    | Halfword memory to register           |

|                  | load half unsigned               | lhu \$s1,20(\$s2)   | \$s1 = Memory[\$s2 + 20]                    | Halfword memory to register           |

|                  | store half                       | sh \$s1,20(\$s2)    | Memory[\$s2 + 20] = \$s1                    | Halfword register to memory           |

| Data<br>transfer | load byte                        | lb \$s1,20(\$s2)    | \$s1 = Memory[\$s2 + 20]                    | Byte from memory to register          |

| tialisiei        | load byte unsigned               | lbu \$s1,20(\$s2)   | \$s1 = Memory[\$s2 + 20]                    | Byte from memory to register          |

|                  | store byte                       | sb \$s1,20(\$s2)    | Memory[\$s2 + 20] = \$s1                    | Byte from register to memory          |

|                  | load linked word                 | 11 \$s1,20(\$s2)    | \$s1 = Memory[\$s2 + 20]                    | Load word as 1st half of atomic swap  |

|                  | store condition. word            | sc \$s1,20(\$s2)    | Memory[\$s2+20]=\$s1;\$s1=0 or 1            | Store word as 2nd half of atomic swap |

|                  | load upper immed.                | lui \$s1,20         | \$s1 = 20 * 2 <sup>16</sup>                 | Loads constant in upper 16 bits       |

|                  | and                              | and \$s1,\$s2,\$s3  | \$s1 = \$s2 & \$s3                          | Three reg. operands; bit-by-bit AND   |

|                  | or                               | or \$s1,\$s2,\$s3   | \$s1 = \$s2   \$s3                          | Three reg. operands; bit-by-bit OR    |

|                  | nor                              | nor \$s1,\$s2,\$s3  | \$s1 = ~ (\$s2   \$s3)                      | Three reg. operands; bit-by-bit NOR   |

| Logical          | and immediate                    | andi \$s1,\$s2,20   | \$s1 = \$s2 & 20                            | Bit-by-bit AND reg with constant      |

| Logical          | or immediate                     | ori \$s1,\$s2,20    | \$s1 = \$s2   <b>20</b>                     | Bit-by-bit OR reg with constant       |

|                  | shift left logical               | sll \$s1,\$s2,10    | \$s1 = \$s2 << <b>10</b>                    | Shift left by constant                |

|                  | shift right logical              | srl \$s1,\$s2,10    | \$s1 = \$s2 >> <b>10</b>                    | Shift right by constant               |

|                  | branch on equal                  | beq \$s1,\$s2,25    | if (\$s1 == \$s2) go to<br>PC + 4 + 100     | Equal test; PC-relative branch        |

|                  | branch on not equal              | bne \$s1,\$s2,25    | if (\$s1!= \$s2) go to<br>PC + 4 + 100      | Not equal test; PC-relative           |

| Conditional      | set on less than                 | slt \$s1,\$s2,\$s3  | if (\$s2 < \$s3) \$s1 = 1;<br>else \$s1 = 0 | Compare less than; for beq, bne       |

| branch           | set on less than unsigned        | sltu \$s1,\$s2,\$s3 | if (\$s2 < \$s3) \$s1 = 1;<br>else \$s1 = 0 | Compare less than unsigned            |

|                  | set less than immediate          | slti \$s1,\$s2,20   | if (\$s2 < 20) \$s1 = 1;<br>else \$s1 = 0   | Compare less than constant            |

|                  | set less than immediate unsigned | sltiu \$s1,\$s2,20  | if (\$s2 < 20) \$s1 = 1;<br>else \$s1 = 0   | Compare less than constant unsigned   |

| 11 892 1         | jump                             | j 2500              | go to 10000                                 | Jump to target address                |

| Unconditional .  | jump register                    | jr \$ra             | go to \$ra                                  | For switch, procedure return          |

| jump             | jump and link                    | jal 2500            | \$ra = PC + 4; go to 10000                  | For procedure call                    |

**FIGURE 2.1** MIPS assembly language revealed in this chapter. This information is also found in Column 1 of the MIPS Reference Data Card at the front of this book.

The natural number of operands for an operation like addition is three: the two numbers being added together and a place to put the sum. Requiring every instruction to have exactly three operands, no more and no less, conforms to the philosophy of keeping the hardware simple: hardware for a variable number of operands is more complicated than hardware for a fixed number. This situation illustrates the first of four underlying principles of hardware design:

Design Principle 1: Simplicity favors regularity.

We can now show, in the two examples that follow, the relationship of programs written in higher-level programming languages to programs in this more primitive notation.

#### **Compiling Two C Assignment Statements into MIPS**

This segment of a C program contains the five variables a, b, c, d, and e. Since Java evolved from C, this example and the next few work for either high-level programming language:

**EXAMPLE**

```

a = b + c;

d = a - e;

```

The translation from C to MIPS assembly language instructions is performed by the *compiler*. Show the MIPS code produced by a compiler.

A MIPS instruction operates on two source operands and places the result in one destination operand. Hence, the two simple statements above compile directly into these two MIPS assembly language instructions:

**ANSWER**

```

add a, b, c sub d, a, e

```

#### **Compiling a Complex C Assignment into MIPS**

A somewhat complex statement contains the five variables f, g, h, i, and j:

$$f = (q + h) - (i + j);$$

**EXAMPLE**

What might a C compiler produce?

#### **ANSWER**

The compiler must break this statement into several assembly instructions, since only one operation is performed per MIPS instruction. The first MIPS instruction calculates the sum of g and h. We must place the result somewhere, so the compiler creates a temporary variable, called  $t\ 0$ :

```

add t0,g,h \# temporary variable t0 contains g + h

```

Although the next operation is subtract, we need to calculate the sum of i and j before we can subtract. Thus, the second instruction places the sum of i and j in another temporary variable created by the compiler, called t1:

```

add t1,i,j # temporary variable t1 contains i + j

```

Finally, the subtract instruction subtracts the second sum from the first and places the difference in the variable f, completing the compiled code:

```

sub f,t0,t1 \# f gets t0 - t1, which is (g + h) - (i + j)

```

## **Check Yourself**

For a given function, which programming language likely takes the most lines of code? Put the three representations below in order.

- 1. Java

- 2. C

- 3. MIPS assembly language

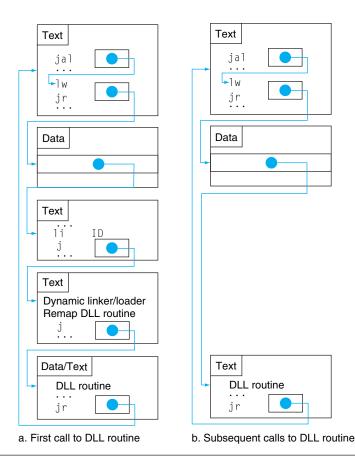

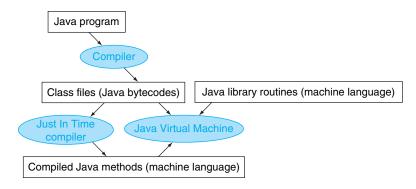

**Elaboration:** To increase portability, Java was originally envisioned as relying on a software interpreter. The instruction set of this interpreter is called *Java bytecodes* (see Section 2.15 on the CD), which is quite different from the MIPS instruction set. To get performance close to the equivalent C program, Java systems today typically compile Java bytecodes into the native instruction sets like MIPS. Because this compilation is normally done much later than for C programs, such Java compilers are often called *Just In Time* (JIT) compilers. Section 2.12 shows how JITs are used later than C compilers in the start-up process, and Section 2.13 shows the performance consequences of compiling versus interpreting Java programs.

## **Operands of the Computer Hardware**

Unlike programs in high-level languages, the operands of arithmetic instructions are restricted; they must be from a limited number of special locations built directly in hardware called *registers*. Registers are primitives used in hardware design that

are also visible to the programmer when the computer is completed, so you can think of registers as the bricks of computer construction. The size of a register in the MIPS architecture is 32 bits; groups of 32 bits occur so frequently that they are given the name **word** in the MIPS architecture.

One major difference between the variables of a programming language and registers is the limited number of registers, typically 32 on current computers, like MIPS. (See Section 2.20 on the CD for the history of the number of registers.) Thus, continuing in our top-down, stepwise evolution of the symbolic representation of the MIPS language, in this section we have added the restriction that the three operands of MIPS arithmetic instructions must each be chosen from one of the 32 32-bit registers.

The reason for the limit of 32 registers may be found in the second of our four underlying design principles of hardware technology:

Design Principle 2: Smaller is faster.

A very large number of registers may increase the clock cycle time simply because it takes electronic signals longer when they must travel farther.

Guidelines such as "smaller is faster" are not absolutes; 31 registers may not be faster than 32. Yet, the truth behind such observations causes computer designers to take them seriously. In this case, the designer must balance the craving of programs for more registers with the designer's desire to keep the clock cycle fast. Another reason for not using more than 32 is the number of bits it would take in the instruction format, as Section 2.5 demonstrates.

Chapter 4 shows the central role that registers play in hardware construction; as we shall see in this chapter, effective use of registers is critical to program performance.

Although we could simply write instructions using numbers for registers, from 0 to 31, the MIPS convention is to use two-character names following a dollar sign to represent a register. Section 2.8 will explain the reasons behind these names. For now, we will use \$\$0,\$\$1,... for registers that correspond to variables in C and Java programs and \$\$t0, \$\$t1,... for temporary registers needed to compile the program into MIPS instructions.

## Compiling a C Assignment Using Registers

It is the compiler's job to associate program variables with registers. Take, for instance, the assignment statement from our earlier example:

$$f = (g + h) - (i + j);$$

The variables f, g, h, i, and j are assigned to the registers \$50, \$51, \$52, \$53, and \$54, respectively. What is the compiled MIPS code?

word The natural unit of access in a computer, usually a group of 32 bits; corresponds to the size of a register in the MIPS architecture.

**EXAMPLE**

#### **ANSWER**

The compiled program is very similar to the prior example, except we replace the variables with the register names mentioned above plus two temporary registers, \$t0 and \$t1, which correspond to the temporary variables above:

```

add 0,51,52 # register 00 contains g + h0 add 1,53,54 # register 10 contains i + j0 sub 50,514 # f gets 10 - 11, which is 11 which is 12 register 13 sub 14 register 15 sub 15 register 16 register 17 sub 18 register 19 register 1

```

#### **Memory Operands**

Programming languages have simple variables that contain single data elements, as in these examples, but they also have more complex data structures—arrays and structures. These complex data structures can contain many more data elements than there are registers in a computer. How can a computer represent and access such large structures?

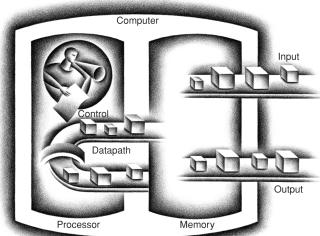

Recall the five components of a computer introduced in Chapter 1 and repeated on page 75. The processor can keep only a small amount of data in registers, but computer memory contains billions of data elements. Hence, data structures (arrays and structures) are kept in memory.

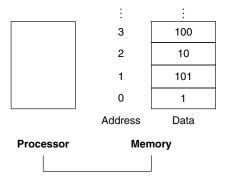

As explained above, arithmetic operations occur only on registers in MIPS instructions; thus, MIPS must include instructions that transfer data between memory and registers. Such instructions are called **data transfer instructions**. To access a word in memory, the instruction must supply the memory **address**. Memory is just a large, single-dimensional array, with the address acting as the index to that array, starting at 0. For example, in Figure 2.2, the address of the third data element is 2, and the value of Memory[2] is 10.

## data transfer instruction

A command that moves data between memory and registers.

address A value used to delineate the location of a specific data element within a memory array.

**FIGURE 2.2 Memory addresses and contents of memory at those locations.** If these elements were words, these addresses would be incorrect, since MIPS actually uses byte addressing, with each word representing four bytes. Figure 2.3 shows the memory addressing for sequential word addresses.

The data transfer instruction that copies data from memory to a register is traditionally called *load*. The format of the load instruction is the name of the operation followed by the register to be loaded, then a constant and register used to access memory. The sum of the constant portion of the instruction and the contents of the second register forms the memory address. The actual MIPS name for this instruction is <code>lw</code>, standing for *load word*.

#### **Compiling an Assignment When an Operand Is in Memory**

Let's assume that A is an array of 100 words and that the compiler has associated the variables g and h with the registers \$\$1 and \$\$2\$ as before. Let's also assume that the starting address, or *base address*, of the array is in \$\$3. Compile this C assignment statement:

**EXAMPLE**

```

g = h + A[8];

```

Although there is a single operation in this assignment statement, one of the operands is in memory, so we must first transfer A[8] to a register. The address of this array element is the sum of the base of the array A, found in register \$53, plus the number to select element 8. The data should be placed in a temporary register for use in the next instruction. Based on Figure 2.2, the first compiled instruction is

**ANSWER**

```

1w $t0,8($s3) # Temporary reg $t0 gets A[8]

```

(On the next page we'll make a slight adjustment to this instruction, but we'll use this simplified version for now.) The following instruction can operate on the value in t0 (which equals A[8]) since it is in a register. The instruction must add t0 (contained in t0) to A[8] (t0) and put the sum in the register corresponding to g (associated with t0):

add

$$$s1,$s2,$t0 # g = h + A[8]$$

The constant in a data transfer instruction (8) is called the *offset*, and the register added to form the address (\$\$3) is called the *base register*.

## Hardware/ Software Interface

alignment restriction

A requirement that data be aligned in memory on natural boundaries. In addition to associating variables with registers, the compiler allocates data structures like arrays and structures to locations in memory. The compiler can then place the proper starting address into the data transfer instructions.

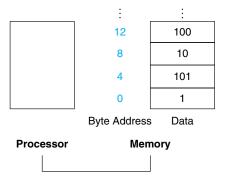

Since 8-bit *bytes* are useful in many programs, most architectures address individual bytes. Therefore, the address of a word matches the address of one of the 4 bytes within the word, and addresses of sequential words differ by 4. For example, Figure 2.3 shows the actual MIPS addresses for the words in Figure 2.2; the byte address of the third word is 8.

In MIPS, words must start at addresses that are multiples of 4. This requirement is called an **alignment restriction**, and many architectures have it. (Chapter 4 suggests why alignment leads to faster data transfers.)

Computers divide into those that use the address of the leftmost or "big end" byte as the word address versus those that use the rightmost or "little end" byte. MIPS is in the *big-endian* camp. (Appendix B, shows the two options to number bytes in a word.)

Byte addressing also affects the array index. To get the proper byte address in the code above, *the offset to be added to the base register* \$s3 *must be*  $4 \times 8$ , *or* 32, so that the load address will select A[8] and not A[8/4]. (See the related pitfall on page 175 of Section 2.18.)

**FIGURE 2.3 Actual MIPS memory addresses and contents of memory for those words.** The changed addresses are highlighted to contrast with Figure 2.2. Since MIPS addresses each byte, word addresses are multiples of 4: there are 4 bytes in a word.

The instruction complementary to load is traditionally called *store*; it copies data from a register to memory. The format of a store is similar to that of a load: the name of the operation, followed by the register to be stored, then offset to select the array element, and finally the base register. Once again, the MIPS address is specified in part by a constant and in part by the contents of a register. The actual MIPS name is SW, standing for *store word*.

#### **Compiling Using Load and Store**

Assume variable h is associated with register \$52 and the base address of the array A is in \$53. What is the MIPS assembly code for the C assignment statement below?

**EXAMPLE**

```

A[12] = h + A[8];

```

Although there is a single operation in the C statement, now two of the operands are in memory, so we need even more MIPS instructions. The first two instructions are the same as the prior example, except this time we use the proper offset for byte addressing in the load word instruction to select A[8], and the add instruction places the sum in \$t0:

**ANSWER**

```

lw $t0,32($s3) # Temporary reg $t0 gets A[8] add $t0,$s2,$t0 # Temporary reg $t0 gets h + A[8]

```

The final instruction stores the sum into A[12], using 48 ( $4 \times 12$ ) as the offset and register \$53 as the base register.

```

sw $t0,48($s3) # Stores h + A[8] back into A[12]

```

Load word and store word are the instructions that copy words between memory and registers in the MIPS architecture. Other brands of computers use other instructions along with load and store to transfer data. An architecture with such alternatives is the Intel x86, described in Section 2.17.

## Hardware/ Software Interface

Many programs have more variables than computers have registers. Consequently, the compiler tries to keep the most frequently used variables in registers and places the rest in memory, using loads and stores to move variables between registers and memory. The process of putting less commonly used variables (or those needed later) into memory is called *spilling* registers.

The hardware principle relating size and speed suggests that memory must be slower than registers, since there are fewer registers. This is indeed the case; data accesses are faster if data is in registers instead of memory.

Moreover, data is more useful when in a register. A MIPS arithmetic instruction can read two registers, operate on them, and write the result. A MIPS data transfer instruction only reads one operand or writes one operand, without operating on it.

Thus, registers take less time to access *and* have higher throughput than memory, making data in registers both faster to access and simpler to use. Accessing registers also uses less energy than accessing memory. To achieve highest performance and conserve energy, compilers must use registers efficiently.

#### **Constant or Immediate Operands**

Many times a program will use a constant in an operation—for example, incrementing an index to point to the next element of an array. In fact, more than half of the MIPS arithmetic instructions have a constant as an operand when running the SPEC2006 benchmarks.

Using only the instructions we have seen so far, we would have to load a constant from memory to use one. (The constants would have been placed in memory when the program was loaded.) For example, to add the constant 4 to register \$53, we could use the code

```

lw $t0, AddrConstant4($s1) \# $t0 = constant 4 add $s3,$s3,$t0 \# $s3 = $s3 + $t0 ($t0 == 4)

```

assuming that \$\$1 + AddrConstant4 is the memory address of the constant 4.

An alternative that avoids the load instruction is to offer versions of the arithmetic instructions in which one operand is a constant. This quick add instruction with one constant operand is called *add immediate* or addi. To add 4 to register \$\$3, we just write

```

addi $s3,$s3,4 $\sharp$s3 = $s3 + 4

```

Immediate instructions illustrate the third hardware design principle, first mentioned in the Fallacies and Pitfalls of Chapter 1:

Design Principle 3: Make the common case fast.

Constant operands occur frequently, and by including constants inside arithmetic instructions, operations are much faster and use less energy than if constants were loaded from memory.

The constant zero has another role, which is to simplify the instruction set by offering useful variations. For example, the move operation is just an add instruction where one operand is zero. Hence, MIPS dedicates a register \$zero to be hardwired to the value zero. (As you might expect, it is register number 0.)

Given the importance of registers, what is the rate of increase in the number of registers in a chip over time?

- 1. Very fast: They increase as fast as Moore's law, which predicts doubling the number of transistors on a chip every 18 months.

- 2. Very slow: Since programs are usually distributed in the language of the computer, there is inertia in instruction set architecture, and so the number of registers increases only as fast as new instruction sets become viable.

**Elaboration:** Although the MIPS registers in this book are 32 bits wide, there is a 64-bit version of the MIPS instruction set with 32 64-bit registers. To keep them straight, they are officially called MIPS-32 and MIPS-64. In this chapter, we use a subset of MIPS-32. Appendix E shows the differences between MIPS-32 and MIPS-64.

The MIPS offset plus base register addressing is an excellent match to structures as well as arrays, since the register can point to the beginning of the structure and the offset can select the desired element. We'll see such an example in Section 2.13.

The register in the data transfer instructions was originally invented to hold an index of an array with the offset used for the starting address of an array. Thus, the base register is also called the *index register*. Today's memories are much larger and the software model of data allocation is more sophisticated, so the base address of the array is normally passed in a register since it won't fit in the offset, as we shall see.

Since MIPS supports negative constants, there is no need for subtract immediate in MIPS.

# 2.4

## **Signed and Unsigned Numbers**

First, let's quickly review how a computer represents numbers. Humans are taught to think in base 10, but numbers may be represented in any base. For example, 123 base 10 = 1111011 base 2.

Numbers are kept in computer hardware as a series of high and low electronic signals, and so they are considered base 2 numbers. (Just as base 10 numbers are called *decimal* numbers, base 2 numbers are called *binary* numbers.)

A single digit of a binary number is thus the "atom" of computing, since all information is composed of binary digits or bits. This fundamental building block

#### Check Yourself

binary digit Also called binary bit. One of the two numbers in base 2, 0 or 1, that are the components of information.

can be one of two values, which can be thought of as several alternatives: high or low, on or off, true or false, or 1 or 0.

Generalizing the point, in any number base, the value of *i*th digit *d* is

$$d \times \text{Base}^i$$

where *i* starts at 0 and increases from right to left. This leads to an obvious way to number the bits in the word: simply use the power of the base for that bit. We subscript decimal numbers with *ten* and binary numbers with *two*. For example,

represents

$$(1 \times 2^3)$$

+  $(0 \times 2^2)$  +  $(1 \times 2^1)$  +  $(1 \times 2^0)_{\text{ten}}$

=  $(1 \times 8)$  +  $(0 \times 4)$  +  $(1 \times 2)$  +  $(1 \times 1)_{\text{ten}}$

=  $8$  +  $0$  +  $2$  +  $1_{\text{ten}}$

We number the bits  $0, 1, 2, 3, \ldots$  from *right to left* in a word. The drawing below shows the numbering of bits within a MIPS word and the placement of the number  $1011_{two}$ :

| 31 | 30             | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 0  | 0              | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 |

|    | (32 bits wide) |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

Since words are drawn vertically as well as horizontally, leftmost and rightmost may be unclear. Hence, the phrase **least significant bit** is used to refer to the rightmost bit (bit 0 above) and **most significant bit** to the leftmost bit (bit 31).

The MIPS word is 32 bits long, so we can represent  $2^{32}$  different 32-bit patterns. It is natural to let these combinations represent the numbers from 0 to  $2^{32} - 1$  (4,294,967,295<sub>ten</sub>):

That is, 32-bit binary numbers can be represented in terms of the bit value times a power of 2 (here xi means the ith bit of x):

least significant bit

MIPS word.

MIPS word.

The rightmost bit in a

most significant bit The leftmost bit in a

$$(x31 \times 2^{31}) + (x30 \times 2^{30}) + (x29 \times 2^{29}) + \ldots + (x1 \times 2^{1}) + (x0 \times 2^{0})$$

Keep in mind that the binary bit patterns above are simply *representatives* of numbers. Numbers really have an infinite number of digits, with almost all being 0 except for a few of the rightmost digits. We just don't normally show leading 0s.

Hardware can be designed to add, subtract, multiply, and divide these binary bit patterns. If the number that is the proper result of such operations cannot be represented by these rightmost hardware bits, *overflow* is said to have occurred. It's up to the programming language, the operating system, and the program to determine what to do if overflow occurs.

Computer programs calculate both positive and negative numbers, so we need a representation that distinguishes the positive from the negative. The most obvious solution is to add a separate sign, which conveniently can be represented in a single bit; the name for this representation is *sign and magnitude*.

Alas, sign and magnitude representation has several shortcomings. First, it's not obvious where to put the sign bit. To the right? To the left? Early computers tried both. Second, adders for sign and magnitude may need an extra step to set the sign because we can't know in advance what the proper sign will be. Finally, a separate sign bit means that sign and magnitude has both a positive and a negative zero, which can lead to problems for inattentive programmers. As a result of these shortcomings, sign and magnitude representation was soon abandoned.

In the search for a more attractive alternative, the question arose as to what would be the result for unsigned numbers if we tried to subtract a large number from a small one. The answer is that it would try to borrow from a string of leading 0s, so the result would have a string of leading 1s.

Given that there was no obvious better alternative, the final solution was to pick the representation that made the hardware simple: leading 0s mean positive, and leading 1s mean negative. This convention for representing signed binary numbers is called *two's complement* representation:

The positive half of the numbers, from 0 to 2,147,483,647 $_{\rm ten}$  ( $2^{31}-1$ ), use the same representation as before. The following bit pattern ( $1000\dots0000_{\rm two}$ ) represents the most negative number  $-2,147,483,648_{\rm ten}$  ( $-2^{31}$ ). It is followed by a declining set of negative numbers:  $-2,147,483,647_{\rm ten}$  ( $1000\dots0001_{\rm two}$ ) down to  $-1_{\rm ten}$  ( $1111\dots1111_{\rm two}$ ).

Two's complement does have one negative number, -2,147,483,648<sub>ten</sub>, that has no corresponding positive number. Such imbalance was also a worry to the inattentive programmer, but sign and magnitude had problems for both the programmer *and* the hardware designer. Consequently, every computer today uses two's complement binary representations for signed numbers.

Two's complement representation has the advantage that all negative numbers have a 1 in the most significant bit. Consequently, hardware needs to test only this bit to see if a number is positive or negative (with the number 0 considered positive). This bit is often called the *sign bit*. By recognizing the role of the sign bit, we can represent positive and negative 32-bit numbers in terms of the bit value times a power of 2:

$$(x31 \times -2^{31}) + (x30 \times 2^{30}) + (x29 \times 2^{29}) + \ldots + (x1 \times 2^{1}) + (x0 \times 2^{0})$$

The sign bit is multiplied by  $-2^{31}$ , and the rest of the bits are then multiplied by positive versions of their respective base values.

#### **Binary to Decimal Conversion**

What is the decimal value of this 32-bit two's complement number?

1111 1111 1111 1111 1111 1111 1111

$$1100_{two}$$

Substituting the number's bit values into the formula above:

$$(1 \times -2^{31}) + (1 \times 2^{30}) + (1 \times 2^{29}) + \dots + (1 \times 2^{2}) + (0 \times 2^{1}) + (0 \times 2^{0})$$

=  $-2^{31} + 2^{30} + 2^{29} + \dots + 2^{2} + 0 + 0$

=  $-2,147,483,648_{\text{ten}} + 2,147,483,644_{\text{ten}}$

=  $-4$

We'll see a shortcut to simplify conversion from negative to positive soon.

Just as an operation on unsigned numbers can overflow the capacity of hardware to represent the result, so can an operation on two's complement numbers. Overflow occurs when the leftmost retained bit of the binary bit pattern is not the same as the infinite number of digits to the left (the sign bit is incorrect): a 0 on the left of the bit pattern when the number is negative or a 1 when the number is positive.

**EXAMPLE**

**ANSWER**

Unlike the numbers discussed above, memory addresses naturally start at 0 and continue to the largest address. Put another way, negative addresses make no sense. Thus, programs want to deal sometimes with numbers that can be positive or negative and sometimes with numbers that can be only positive. Some programming languages reflect this distinction. C, for example, names the former *integers* (declared as int in the program) and the latter *unsigned integers* (unsigned int). Some C style guides even recommend declaring the former as signed int to keep the distinction clear.

## Hardware/ Software Interface

Let's examine two useful shortcuts when working with two's complement numbers. The first shortcut is a quick way to negate a two's complement binary number. Simply invert every 0 to 1 and every 1 to 0, then add one to the result. This shortcut is based on the observation that the sum of a number and its inverted representation must be  $111 \dots 111_{\text{two}}$ , which represents -1. Since  $x + \overline{x} = -1$ , therefore  $x + \overline{x} + 1 = 0$  or  $\overline{x} + 1 = -x$ .

#### **Negation Shortcut**

Negate  $2_{ten}$ , and then check the result by negating  $-2_{ten}$ .

$2_{\text{ten}} = 0000\ 0000\ 0000\ 0000\ 0000\ 0000\ 0000\ 0010_{\text{two}}$

Negating this number by inverting the bits and adding one,

**EXAMPLE**

**ANSWER**

Going the other direction,

is first inverted and then incremented:

Our next shortcut tells us how to convert a binary number represented in *n* bits to a number represented with more than *n* bits. For example, the immediate field in the load, store, branch, add, and set on less than instructions contains a two's complement 16-bit number, representing  $-32,768_{\text{ten}}$  ( $-2^{15}$ ) to  $32,767_{\text{ten}}$  ( $2^{15}-1$ ). To add the immediate field to a 32-bit register, the computer must convert that 16-bit number to its 32-bit equivalent. The shortcut is to take the most significant bit from the smaller quantity—the sign bit—and replicate it to fill the new bits of the larger quantity. The old bits are simply copied into the right portion of the new word. This shortcut is commonly called *sign extension*.

**EXAMPLE**

**ANSWER**

Convert 16-bit binary versions of  $2_{ten}$  and  $-2_{ten}$  to 32-bit binary numbers.

The 16-bit binary version of the number 2 is

$$0000\ 0000\ 0000\ 0010_{two} = 2_{ten}$$

It is converted to a 32-bit number by making 16 copies of the value in the most significant bit (0) and placing that in the left-hand half of the word. The right half gets the old value:

$0000\ 0000\ 0000\ 0000\ 0000\ 0000\ 0000\ 0010_{two} = 2_{ten}$

Let's negate the 16-bit version of 2 using the earlier shortcut. Thus,

$$0000\ 0000\ 0000\ 0010_{two}$$

becomes

Creating a 32-bit version of the negative number means copying the sign bit 16 times and placing it on the left:

This trick works because positive two's complement numbers really have an infinite number of 0s on the left and negative two's complement numbers have an infinite number of 1s. The binary bit pattern representing a number hides leading bits to fit the width of the hardware; sign extension simply restores some of them.

## **Summary**

The main point of this section is that we need to represent both positive and negative integers within a computer word, and although there are pros and cons to any option, the overwhelming choice since 1965 has been two's complement.

What is the decimal value of this 64-bit two's complement number?

**Check Yourself**

$$1) -4_{ten}$$

$$3) -16_{ten}$$

**Elaboration:** Two's complement gets its name from the rule that the unsigned sum of an n-bit number and its negative is  $2^n$ ; hence, the complement or negation of a two's complement number x is  $2^n - x$ .

#### one's complement

A notation that represents the most negative value by  $10 \dots 000_{two}$  and the most positive value by  $01 \dots 11_{two}$ , leaving an equal number of negatives and positives but ending up with two zeros, one positive  $(00 \dots 00_{two})$  and one negative  $(11 \dots 11_{two})$ . The term is also used to mean the inversion of every bit in a pattern: 0 to 1 and 1 to 0.

#### biased notation

A notation that represents the most negative value by  $00...000_{two}$  and the most positive value by  $11...11_{two}$ , with 0 typically having the value  $10...00_{two}$ , thereby biasing the number such that the number plus the bias has a nonnegative representation.

A third alternative representation to two's complement and sign and magnitude is called one's complement. The negative of a one's complement is found by inverting each bit, from 0 to 1 and from 1 to 0, which helps explain its name since the complement of x is  $2^n - x - 1$ . It was also an attempt to be a better solution than sign and magnitude, and several early scientific computers did use the notation. This representation is similar to two's complement except that it also has two 0s:  $00 \dots 00_{\text{two}}$  is positive 0 and  $11 \dots 11_{\text{two}}$  is negative 0. The most negative number,  $10 \dots 000_{\text{two}}$ , represents  $-2,147,483,647_{\text{ten}}$ , and so the positives and negatives are balanced. One's complement adders did need an extra step to subtract a number, and hence two's complement dominates today.

A final notation, which we will look at when we discuss floating point in Chapter 3, is to represent the most negative value by  $00\ldots000_{two}$  and the most positive value by  $11\ldots11_{two}$ , with 0 typically having the value  $10\ldots00_{two}$ . This is called a biased notation, since it biases the number such that the number plus the bias has a nonnegative representation.

**Elaboration:** For signed decimal numbers, we used "-" to represent negative because there are no limits to the size of a decimal number. Given a fixed word size, binary and hexadecimal (see Figure 2.4) bit strings can encode the sign; hence we do not normally use "+" or "-" with binary or hexadecimal notation.

## **Representing Instructions in the Computer**

We are now ready to explain the difference between the way humans instruct computers and the way computers see instructions.

Instructions are kept in the computer as a series of high and low electronic signals and may be represented as numbers. In fact, each piece of an instruction can be considered as an individual number, and placing these numbers side by side forms the instruction.

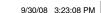

Since registers are referred to by almost all instructions, there must be a convention to map register names into numbers. In MIPS assembly language, registers \$50 to \$57 map onto registers 16 to 23, and registers \$t0 to \$t7 map onto registers 8 to 15. Hence, \$50 means register 16, \$51 means register 17, \$52 means register 18,..., \$t0 means register 8, \$t1 means register 9, and so on. We'll describe the convention for the rest of the 32 registers in the following sections.

#### **Translating a MIPS Assembly Instruction into a Machine Instruction**

Let's do the next step in the refinement of the MIPS language as an example. We'll show the real MIPS language version of the instruction represented symbolically as

**EXAMPLE**

add \$t0,\$s1,\$s2

first as a combination of decimal numbers and then of binary numbers.

The decimal representation is

| 0 | 17 | 18 | 8 | 0 | 32 |

|---|----|----|---|---|----|

Each of these segments of an instruction is called a *field*. The first and last fields (containing 0 and 32 in this case) in combination tell the MIPS computer that this instruction performs addition. The second field gives the number of the register that is the first source operand of the addition operation (17 = \$\$1), and the third field gives the other source operand for the addition (18 = \$\$2). The fourth field contains the number of the register that is to receive the sum (8 = \$t0). The fifth field is unused in this instruction, so it is set to 0. Thus, this instruction adds register \$\$1 to register \$3 and places the sum in register \$5.

This instruction can also be represented as fields of binary numbers as opposed to decimal:

| 000000 | 10001  | 10010  | 01000  | 00000  | 100000 |

|--------|--------|--------|--------|--------|--------|

| 6 bits | 5 bits | 5 bits | 5 bits | 5 bits | 6 bits |

This layout of the instruction is called the **instruction format**. As you can see from counting the number of bits, this MIPS instruction takes exactly 32 bits—the same size as a data word. In keeping with our design principle that simplicity favors regularity, all MIPS instructions are 32 bits long.

To distinguish it from assembly language, we call the numeric version of instructions **machine language** and a sequence of such instructions *machine code*.

It would appear that you would now be reading and writing long, tedious strings of binary numbers. We avoid that tedium by using a higher base than binary that converts easily into binary. Since almost all computer data sizes are multiples of 4, hexadecimal (base 16) numbers are popular. Since base 16 is a power of 2, we can trivially convert by replacing each group of four binary digits by a single hexadecimal digit, and vice versa. Figure 2.4 converts between hexadecimal and binary.

## **ANSWER**

instruction format

A form of representation of an instruction composed of fields of binary numbers.

#### machine language

Binary representation used for communication within a computer system.

hexadecimal

Numbers in base 16.

**EXAMPLE**

**ANSWER**

| Hexadecimal      | Binary              | Hexadecimal      | Binary              | Hexadecimal      | Binary              | Hexadecimal      | Binary              |

|------------------|---------------------|------------------|---------------------|------------------|---------------------|------------------|---------------------|

| O <sub>hex</sub> | 0000 <sub>two</sub> | 4 <sub>hex</sub> | 0100 <sub>two</sub> | 8 <sub>hex</sub> | 1000 <sub>two</sub> | c <sub>hex</sub> | 1100 <sub>two</sub> |

| 1 <sub>hex</sub> | 0001 <sub>two</sub> | 5 <sub>hex</sub> | 0101 <sub>two</sub> | 9 <sub>hex</sub> | 1001 <sub>two</sub> | d <sub>hex</sub> | 1101 <sub>two</sub> |

| 2 <sub>hex</sub> | 0010 <sub>two</sub> | 6 <sub>hex</sub> | 0110 <sub>two</sub> | a <sub>hex</sub> | 1010 <sub>two</sub> | e <sub>hex</sub> | 1110 <sub>two</sub> |

| 3 <sub>hex</sub> | 0011 <sub>two</sub> | 7 <sub>hex</sub> | 0111 <sub>two</sub> | b <sub>hex</sub> | 1011 <sub>two</sub> | f <sub>hex</sub> | 1111 <sub>two</sub> |

**FIGURE 2.4 The hexadecimal-binary conversion table.** Just replace one hexadecimal digit by the corresponding four binary digits, and vice versa. If the length of the binary number is not a multiple of 4, go from right to left.

Because we frequently deal with different number bases, to avoid confusion we will subscript decimal numbers with *ten*, binary numbers with *two*, and hexadecimal numbers with *hex*. (If there is no subscript, the default is base 10.) By the way, C and Java use the notation 0xnnnn for hexadecimal numbers.

#### **Binary to Hexadecimal and Back**

Convert the following hexadecimal and binary numbers into the other base:

$$eca8 6420_{hex}$$

0001 0011 0101 0111 1001 1011 1101 1111<sub>two</sub>

Using Figure 2.4, the answer is just a table lookup one way:

1110 1100 1010 1000 0110 0100 0010 0000<sub>two</sub>

And then the other direction:

#### **MIPS Fields**

MIPS fields are given names to make them easier to discuss:

| 6 bits | 5 bits | 5 bits | 5 bits | 5 bits | 6 bits |

|--------|--------|--------|--------|--------|--------|

| ор     | rs     | rt     | rd     | shamt  | funct  |

Here is the meaning of each name of the fields in MIPS instructions:

- *op:* Basic operation of the instruction, traditionally called the **opcode**.

- *rs:* The first register source operand.

- *rt*: The second register source operand.

- *rd*: The register destination operand. It gets the result of the operation.

- *shamt*: Shift amount. (Section 2.6 explains shift instructions and this term; it will not be used until then, and hence the field contains zero in this section.)

- *funct*: Function. This field, often called the *function code*, selects the specific variant of the operation in the op field.

A problem occurs when an instruction needs longer fields than those shown above. For example, the load word instruction must specify two registers and a constant. If the address were to use one of the 5-bit fields in the format above, the constant within the load word instruction would be limited to only  $2^5$  or 32. This constant is used to select elements from arrays or data structures, and it often needs to be much larger than 32. This 5-bit field is too small to be useful.

Hence, we have a conflict between the desire to keep all instructions the same length and the desire to have a single instruction format. This leads us to the final hardware design principle:

Design Principle 4: Good design demands good compromises.

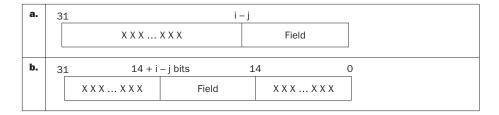

The compromise chosen by the MIPS designers is to keep all instructions the same length, thereby requiring different kinds of instruction formats for different kinds of instructions. For example, the format above is called *R-type* (for register) or *R-format*. A second type of instruction format is called *I-type* (for immediate) or *I-format* and is used by the immediate and data transfer instructions. The fields of I-format are

| ор     | rs     | rt     | constant or address |

|--------|--------|--------|---------------------|

| 6 bits | 5 bits | 5 bits | 16 bits             |

The 16-bit address means a load word instruction can load any word within a region of  $\pm 2^{15}$  or 32,768 bytes ( $\pm 2^{13}$  or 8192 words) of the address in the base register rs. Similarly, add immediate is limited to constants no larger than  $\pm 2^{15}$ . We see that more than 32 registers would be difficult in this format, as the rs and rt fields would each need another bit, making it harder to fit everything in one word. Let's look at the load word instruction from page 83:

1w \$t0,32(\$s3) # Temporary reg \$t0 gets A[8]

opcode The field that denotes the operation and format of an instruction.

Here, 19 (for \$\$3) is placed in the rs field, 8 (for \$\$10) is placed in the rt field, and 32 is placed in the address field. Note that the meaning of the rt field has changed for this instruction: in a load word instruction, the rt field specifies the *destination* register, which receives the result of the load.

Although multiple formats complicate the hardware, we can reduce the complexity by keeping the formats similar. For example, the first three fields of the R-type and I-type formats are the same size and have the same names; the length of the fourth field in I-type is equal to the sum of the lengths of the last three fields of R-type.

In case you were wondering, the formats are distinguished by the values in the first field: each format is assigned a distinct set of values in the first field (op) so that the hardware knows whether to treat the last half of the instruction as three fields (R-type) or as a single field (I-type). Figure 2.5 shows the numbers used in each field for the MIPS instructions covered here.

| Instruction     | Format | ор                | rs  | rt  | rd   | shamt | funct             | address  |

|-----------------|--------|-------------------|-----|-----|------|-------|-------------------|----------|

| add             | R      | 0                 | reg | reg | reg  | 0     | 32 <sub>ten</sub> | n.a.     |

| sub (subtract)  | R      | 0                 | reg | reg | reg  | 0     | 34 <sub>ten</sub> | n.a.     |

| add immediate   | I      | 8 <sub>ten</sub>  | reg | reg | n.a. | n.a.  | n.a.              | constant |

| ไพ (load word)  | I      | 35 <sub>ten</sub> | reg | reg | n.a. | n.a.  | n.a.              | address  |

| SW (store word) | I      | 43 <sub>ten</sub> | reg | reg | n.a. | n.a.  | n.a.              | address  |

**FIGURE 2.5 MIPS instruction encoding.** In the table above, "reg" means a register number between 0 and 31, "address" means a 16-bit address, and "n.a." (not applicable) means this field does not appear in this format. Note that add and sub instructions have the same value in the op field; the hardware uses the funct field to decide the variant of the operation: add (32) or subtract (34).

#### Translating MIPS Assembly Language into Machine Language

**EXAMPLE**

We can now take an example all the way from what the programmer writes to what the computer executes. If t1 has the base of the array A and s2 corresponds to h, the assignment statement

```

A[300] = h + A[300];

```

is compiled into

```

lw $t0,1200($t1)\# Temporary reg $t0 gets A[300] add $t0,$s2,$t0 \# Temporary reg $t0 gets h + A[300] sw $t0,1200($t1) \# Stores h + A[300] back into A[300]

```

What is the MIPS machine language code for these three instructions?

For convenience, let's first represent the machine language instructions using decimal numbers. From Figure 2.5, we can determine the three machine language instructions:

**ANSWER**

| ор | rs | rt | rd   | address/<br>shamt | funct |  |  |  |  |

|----|----|----|------|-------------------|-------|--|--|--|--|

| 35 | 9  | 8  | 1200 |                   |       |  |  |  |  |

| 0  | 18 | 8  | 8    | 0                 | 32    |  |  |  |  |

| 43 | 9  | 8  |      | 1200              |       |  |  |  |  |

The 1w instruction is identified by 35 (see Figure 2.5) in the first field (op). The base register 9 (\$t1) is specified in the second field (rs), and the destination register 8 (\$t0) is specified in the third field (rt). The offset to select A[300] (1200 = 300 × 4) is found in the final field (address).

The add instruction that follows is specified with 0 in the first field (op) and 32 in the last field (funct). The three register operands (18, 8, and 8) are found in the second, third, and fourth fields and correspond to \$52, \$t0, and \$t0.

The SW instruction is identified with 43 in the first field. The rest of this final instruction is identical to the TW instruction.

Since  $1200_{\text{ten}} = 0000\ 0100\ 1011\ 0000_{\text{two}}$ , the binary equivalent to the decimal form is:

| 100011 | 01001 | 01000 | 0000 0100 1011 0000 |       |        |  |

|--------|-------|-------|---------------------|-------|--------|--|

| 000000 | 10010 | 01000 | 01000               | 00000 | 100000 |  |

| 101011 | 01001 | 01000 | 0000 0100 1011 0000 |       |        |  |

Note the similarity of the binary representations of the first and last instructions. The only difference is in the third bit from the left, which is highlighted here.

Figure 2.6 summarizes the portions of MIPS machine language described in this section. As we shall see in Chapter 4, the similarity of the binary representations of related instructions simplifies hardware design. These similarities are another example of regularity in the MIPS architecture.

#### **MIPS** machine language

| Name       | Format | Example |        |        | Comments             |   |        |                                        |

|------------|--------|---------|--------|--------|----------------------|---|--------|----------------------------------------|

| add        | R      | 0       | 18     | 19     | 17 0 32              |   | 32     | add \$s1,\$s2,\$s3                     |

| sub        | R      | 0       | 18     | 19     | 17                   | 0 | 34     | <b>sub</b> \$s1,\$s2,\$s3              |

| addi       | I      | 8       | 18     | 17     | 100                  |   |        | addi \$s1,\$s2,100                     |

| lw         | I      | 35      | 18     | 17     | 100                  |   |        | lw \$s1,100(\$s2)                      |

| sw         | I      | 43      | 18     | 17     | 100                  |   |        | <b>sw</b> \$s1,100(\$s2)               |

| Field size |        | 6 bits  | 5 bits | 5 bits | 5 bits 5 bits 6 bits |   | 6 bits | All MIPS instructions are 32 bits long |

| R-format   | R      | ор      | rs     | rt     | rd shamt funct       |   | funct  | Arithmetic instruction format          |

| I-format   | ļ      | ор      | rs     | rt     | address              |   |        | Data transfer format                   |

**FIGURE 2.6 MIPS architecture revealed through Section 2.5.** The two MIPS instruction formats so far are R and I. The first 16 bits are the same: both contain an *op* field, giving the base operation; an *rs* field, giving one of the sources; and the *rt* field, which specifies the other source operand, except for load word, where it specifies the destination register. R-format divides the last 16 bits into an *rd* field, specifying the destination register; the *shamt* field, which Section 2.6 explains; and the *funct* field, which specifies the specific operation of R-format instructions. I-format combines the last 16 bits into a single *address* field.

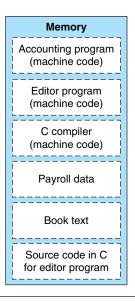

Today's computers are built on two key principles:

- 1. Instructions are represented as numbers.

- 2. Programs are stored in memory to be read or written, just like numbers.

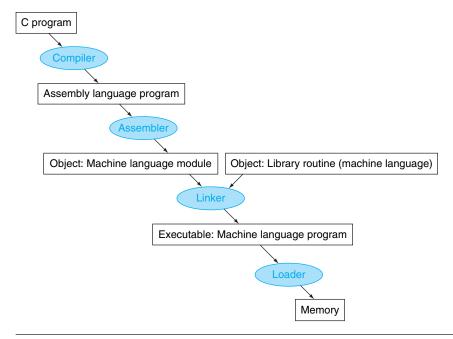

These principles lead to the *stored-program* concept; its invention let the computing genie out of its bottle. Figure 2.7 shows the power of the concept; specifically, memory can contain the source code for an editor program, the corresponding compiled machine code, the text that the compiled program is using, and even the compiler that generated the machine code.

One consequence of instructions as numbers is that programs are often shipped as files of binary numbers. The commercial implication is that computers can inherit ready-made software provided they are compatible with an existing instruction set. Such "binary compatibility" often leads industry to align around a small number of instruction set architectures.

**FIGURE 2.7 The stored-program concept.** Stored programs allow a computer that performs accounting to become, in the blink of an eye, a computer that helps an author write a book. The switch happens simply by loading memory with programs and data and then telling the computer to begin executing at a given location in memory. Treating instructions in the same way as data greatly simplifies both the memory hardware and the software of computer systems. Specifically, the memory technology needed for data can also be used for programs, and programs like compilers, for instance, can translate code written in a notation far more convenient for humans into code that the computer can understand.

What MIPS instruction does this represent? Chose from one of the four options below.

## Check Yourself

| ор | rs | rt | rd | shamt | funct |

|----|----|----|----|-------|-------|

| 0  | 8  | 9  | 10 | 0     | 34    |

- 1. add \$s0, \$s1, \$s2

- 2. add \$s2, \$s0, \$s1

- 3. add \$s2, \$s1, \$s0

- 4. sub \$s2, \$s0, \$s1

"Contrariwise," continued Tweedledee, "if it was so, it might be; and if it were so, it would be; but as it isn't, it ain't. That's logic."

Lewis Carroll, Alice's Adventures in Wonderland, 1865

## **Logical Operations**

Although the first computers operated on full words, it soon became clear that it was useful to operate on fields of bits within a word or even on individual bits. Examining characters within a word, each of which is stored as 8 bits, is one example of such an operation (see Section 2.9). It follows that operations were added to programming languages and instruction set architectures to simplify, among other things, the packing and unpacking of bits into words. These instructions are called logical operations. Figure 2.8 shows logical operations in C, Java, and MIPS.

| Logical operations | C operators | Java operators | MIPS instructions |

|--------------------|-------------|----------------|-------------------|

| Shift left         | <<          | <<             | sll               |

| Shift right        | >>          | >>>            | srl               |

| Bit-by-bit AND     | &           | &              | and, andi         |

| Bit-by-bit OR      |             |                | or, ori           |

| Bit-by-bit NOT     | ~           | ~              | nor               |

**FIGURE 2.8** C and Java logical operators and their corresponding MIPS instructions. MIPS implements NOT using a NOR with one operand being zero.

The first class of such operations is called *shifts*. They move all the bits in a word to the left or right, filling the emptied bits with 0s. For example, if register \$50 contained

$$0000\ 0000\ 0000\ 0000\ 0000\ 0000\ 0000\ 1001_{two} = 9_{ten}$$

and the instruction to shift left by 4 was executed, the new value would be:

0000 0000 0000 0000 0000 0000 1001 0000<sub>two</sub>=

$$144_{ten}$$

The dual of a shift left is a shift right. The actual name of the two MIPS shift instructions are called *shift left logical*(S]]) and *shift right logical*(S]]). The following

instruction performs the operation above, assuming that the original value was in register \$50 and the result should go in register \$t2:

$$$11 $t2,$s0,4 # reg $t2 = reg $s0 \le 4 bits$$

We delayed explaining the *shamt* field in the R-format. Used in shift instructions, it stands for *shift amount*. Hence, the machine language version of the instruction above is

| ор | rs | rt | rd | shamt | funct |

|----|----|----|----|-------|-------|

| 0  | 0  | 16 | 10 | 4     | 0     |

The encoding of sll is 0 in both the op and funct fields, rd contains 10 (register \$t2), rt contains 16 (register \$s0), and shamt contains 4. The rs field is unused and thus is set to 0.

Shift left logical provides a bonus benefit. Shifting left by i bits gives the same result as multiplying by  $2^i$ , just as shifting a decimal number by i digits is equivalent to multiplying by  $10^i$ . For example, the above SII shifts by 4, which gives the same result as multiplying by  $2^4$  or 16. The first bit pattern above represents 9, and  $9 \times 16 = 144$ , the value of the second bit pattern.

Another useful operation that isolates fields is AND. (We capitalize the word to avoid confusion between the operation and the English conjunction.) AND is a bit-by-bit operation that leaves a 1 in the result only if both bits of the operands are 1. For example, if register \$t2 contains

AND A logical bit-bybit operation with two operands that calculates a 1 only if there is a 1 in both operands.

$0000\ 0000\ 0000\ 0000\ 0000\ 1101\ 1100\ 0000_{two}$

and register \$t1 contains

$0000\ 0000\ 0000\ 0000\ 0011\ 1100\ 0000\ 0000_{two}$

then, after executing the MIPS instruction

and

$$$t0,$t1,$t2$$

# reg  $$t0 = reg $t1 & reg $t2$

the value of register \$t0 would be

$0000\ 0000\ 0000\ 0000\ 0000\ 1100\ 0000\ 0000_{two}$

OR A logical bit-bybit operation with two operands that calculates a 1 if there is a 1 in *either* operand. As you can see, AND can apply a bit pattern to a set of bits to force 0s where there is a 0 in the bit pattern. Such a bit pattern in conjunction with AND is traditionally called a *mask*, since the mask "conceals" some bits.

To place a value into one of these seas of 0s, there is the dual to AND, called **OR**. It is a bit-by-bit operation that places a 1 in the result if *either* operand bit is a 1. To elaborate, if the registers \$t1 and \$t2 are unchanged from the preceding example, the result of the MIPS instruction

or

$$$t0,$t1,$t2 # reg $t0 = reg $t1 | reg $t2$$

is this value in register \$t0:

```

0000 0000 0000 0000 0011 1101 1100 0000<sub>two</sub>

```

NOT A logical bit-bybit operation with one operand that inverts the bits; that is, it replaces every 1 with a 0, and every 0 with a 1

every 1 with a 0, and every 0 with a 1.

NOR A logical bit-by-bit operation with two operands that calculates the NOT of the OR of the

two operands. That is, it calculates a 1 only if there

is a 0 in *both* operands.

The final logical operation is a contrarian. **NOT** takes one operand and places a 1 in the result if one operand bit is a 0, and vice versa. In keeping with the three-operand format, the designers of MIPS decided to include the instruction **NOR** (NOT OR) instead of NOT. If one operand is zero, then it is equivalent to NOT: A NOR 0 = NOT (A OR 0 = NOT (A).

If the register \$t1 is unchanged from the preceding example and register \$t3 has the value 0, the result of the MIPS instruction

```

nor $t0,$t1,$t3 # reg $t0 = ~ (reg $t1 | reg $t3)

```

is this value in register \$t0:

Figure 2.8 above shows the relationship between the C and Java operators and the MIPS instructions. Constants are useful in AND and OR logical operations as well as in arithmetic operations, so MIPS also provides the instructions *and immediate* (andi) and *or immediate* (ori). Constants are rare for NOR, since its main use is to invert the bits of a single operand; thus, the MIPS instruction set architecture has no immediate version.

**Elaboration:** The full MIPS instruction set also includes exclusive or (XOR), which sets the bit to 1 when two corresponding bits differ, and to 0 when they are the same. C allows *bit fields* or *fields* to be defined within words, both allowing objects to be

packed within a word and to match an externally enforced interface such as an I/O device. All fields must fit within a single word. Fields are unsigned integers that can be as short as 1 bit. C compilers insert and extract fields using logical instructions in MIPS: and, or, sll, and srl.

Which operations can isolate a field in a word?

- 1. AND

- 2. A shift left followed by a shift right

# 2.7

## **Instructions for Making Decisions**

What distinguishes a computer from a simple calculator is its ability to make decisions. Based on the input data and the values created during computation, different instructions execute. Decision making is commonly represented in programming languages using the *if* statement, sometimes combined with *go to* statements and labels. MIPS assembly language includes two decision-making instructions, similar to an *if* statement with a *go to*. The first instruction is

beg register1, register2, L1

This instruction means go to the statement labeled L1 if the value in register1 equals the value in register2. The mnemonic beq stands for *branch if equal*. The second instruction is

bne register1, register2, L1

It means go to the statement labeled L1 if the value in register1 does *not* equal the value in register2. The mnemonic bne stands for *branch if not equal*. These two instructions are traditionally called **conditional branches**.

## Check Yourself

The utility of an automatic computer lies in the possibility of using a given sequence of instructions repeatedly, the number of times it is iterated being dependent upon the results of the computation....This choice can be made to depend upon the sign of a number (zero being reckoned as plus for machine purposes). Consequently, we introduce an [instruction] (the conditional transfer [instruction]) which will, depending on the sign of a given number, cause the proper one of two routines to be executed. Burks, Goldstine, and

#### conditional branch

von Neumann, 1947

An instruction that requires the comparison of two values and that allows for a subsequent transfer of control to a new address in the program based on the outcome of the comparison.

## **EXAMPLE**

## **ANSWER**

#### Compiling if-then-else into Conditional Branches

In the following code segment, f, g, h, i, and j are variables. If the five variables f through j correspond to the five registers \$50 through \$54, what is the compiled MIPS code for this C *if* statement?

```

if (i == j) f = g + h; else f = g - h;

```

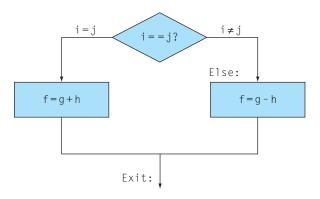

Figure 2.9 is a flowchart of what the MIPS code should do. The first expression compares for equality, so it would seem that we would want the branch if registers are equal instruction (beq). In general, the code will be more efficient if we test for the opposite condition to branch over the code that performs the subsequent *then* part of the if (the label Else is defined below) and so we use the branch if registers are *not* equal instruction (bne):

```

bne \$s3,\$s4,Else # go to Else if i \neq j

```

The next assignment statement performs a single operation, and if all the operands are allocated to registers, it is just one instruction:

```

add \$s0,\$s1,\$s2  # f = g + h (skipped if i \neq j)

```

We now need to go to the end of the *if* statement. This example introduces another kind of branch, often called an *unconditional branch*. This instruction says that the processor always follows the branch. To distinguish between conditional and unconditional branches, the MIPS name for this type of instruction is *jump*, abbreviated as j (the label Exit is defined below).

```

j Exit # go to Exit

```

The assignment statement in the *else* portion of the *if* statement can again be compiled into a single instruction. We just need to append the label Else to this instruction. We also show the label Exit that is after this instruction, showing the end of the *if-then-else* compiled code:

```

Else:sub $s0,$s1,$s2  # f = g - h (skipped if i = j) Exit:

```

**FIGURE 2.9 Illustration of the options in the** *if* **statement above.** The left box corresponds to the *then* part of the *if* statement, and the right box corresponds to the *else* part.

Notice that the assembler relieves the compiler and the assembly language programmer from the tedium of calculating addresses for branches, just as it does for calculating data addresses for loads and stores (see Section 2.12).

Compilers frequently create branches and labels where they do not appear in the programming language. Avoiding the burden of writing explicit labels and branches is one benefit of writing in high-level programming languages and is a reason coding is faster at that level.

## Hardware/ Software Interface

#### Loops

Decisions are important both for choosing between two alternatives—found in *if* statements—and for iterating a computation—found in loops. The same assembly instructions are the building blocks for both cases.

#### Compiling a while Loop in C

Here is a traditional loop in C:

Assume that i and k correspond to registers \$53 and \$55 and the base of the array Save is in \$56. What is the MIPS assembly code corresponding to this C segment?

**EXAMPLE**

#### **ANSWER**

The first step is to load save[i] into a temporary register. Before we can load save[i] into a temporary register, we need to have its address. Before we can add i to the base of array save to form the address, we must multiply the index i by 4 due to the byte addressing problem. Fortunately, we can use shift left logical, since shifting left by 2 bits multiplies by  $2^2$  or 4 (see page 103 in the prior section). We need to add the label loop to it so that we can branch back to that instruction at the end of the loop:

```

Loop: sll $t1,$s3,2 # Temp reg $t1 = i * 4

```

To get the address of save[i], we need to add \$t1 and the base of save in \$s6:

add

$$t1, t1, s6$$

#  $t1 = address of save[i]$

Now we can use that address to load Save[i] into a temporary register:

```

1w $t0,0($t1) # Temp reg $t0 = save[i]

```

The next instruction performs the loop test, exiting if  $save[i] \neq k$ :

bne

$$t0, s5$$

, Exit # go to Exit if save[i]  $\neq k$

The next instruction adds 1 to i:

```

addi $s3,$s3,1 # i = i + 1

```

The end of the loop branches back to the *while* test at the top of the loop. We just add the Exit label after it, and we're done:

(See the exercises for an optimization of this sequence.)

## Hardware/ Software Interface

Such sequences of instructions that end in a branch are so fundamental to compiling that they are given their own buzzword: a **basic block** is a sequence of instructions without branches, except possibly at the end, and without branch targets or branch labels, except possibly at the beginning. One of the first early phases of compilation is breaking the program into basic blocks.

basic block A sequence of instructions without branches (except possibly at the end) and without branch targets or branch labels (except possibly at the beginning).

The test for equality or inequality is probably the most popular test, but sometimes it is useful to see if a variable is less than another variable. For example, a *for* loop may want to test to see if the index variable is less than 0. Such comparisons are accomplished in MIPS assembly language with an instruction that compares two

registers and sets a third register to 1 if the first is less than the second; otherwise, it is set to 0. The MIPS instruction is called set on less than, or Slt. For example,

$$$1t$$

\$t0, \$s3, \$s4  $$\#$t0 = 1 if $s3 < $s4$